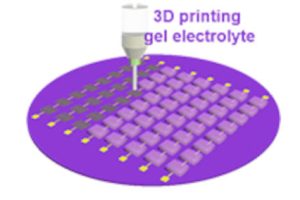

Researchers at the Dalian Institute of Chemical Physics have found a way to deposit micro-supercapacitors consistently on surfaces such as silicon as a way to add energy storage directly to ICs. This is not the first time that supercapacitors have been deposited on such substrates, but the team claims to have combined unpresidented cell density, electrochemical performance and cell-to-cell consistency ...

Research

The latest electronics research news from within the industry and universities from around the world.

10MHz RC oscillator errs ±0.28% over -45 to 125°C

RC oscillators can be small or accurate, and now that can be both after Delft University of Technology*, Silicon Integrated and Tsinghua University revealed a 10MHz RC oscillator with ±0.28% accuracy over -45 to 125°V after a one-point trim, fabricated with a 0.01mm2 footprint in standard 0.18μm CMOS. The scheme avoids needing the need for resistors with opposing temperature coefficients, ...

ISSCC 2023: Class-D audio at -111.2dB THD+N and 120.9dB dynamic range

Class-D audio amplifiers are power efficient, but do not beat, or even match, well-designed Class-AB and Class-A amplifiers on many other specs. This said, Delft University of Technology, working with Goodix Technology, seems to have got right up amongst the hi-fi numbers with a 0.18μm BCD prototype IC that achieves 120.9dB dynamic range and -111.2dB peak THD+N. At full power ...

ISSCC 2023: 1.7Tbit flash IC has five bits per cell

Intel has made a move from four bits per cell to demonstrate a 1.7Tbit NAND flash IC, which it described at ISSCC 2023 this week. Fabricated over 192 layers (cross section, right) of floating gates, the actual capacity is 1.67Tbit, spread over 73.3mm2 – equating to 23.3Gb/mm2 – which can be down-shifted to 1.33Tbit 4bit/cell (18.6Gb/mm2) or 1Tbit 3bit/cell (14.0Gb/mm2) – ...

ISSCC 2023: 2D materials instead of silicon in the angstrom era?

At ISSCC 2023 in San Francisco, Belgian research lab Imec presented transistor designs shrunk beyond the capabilities of silicon. It argued that finfet and gate-all-around designs can only go so far with silicon as, to get fast access to the carriers inside a channel, the channels have to be so thin that physics takes its toll. At <3mn, thickness variations ...

Imec PLL generates FMCW signals for mmWave radar

Imec has come up with a novel digitally calibrated charge-pump (CP) phase-locked loop (PLL) that can generate high-quality frequency-modulated continuous-wave (FMCW) signals for mmWave radars at low power consumption. The novel PLL is a critical building block for future short-range automotive (in-cabin and out-of-cabin) and industrial (e.g., on-cobot sensing) radar applications. FMCW mmWave-based radar sensors are becoming increasingly popular for ...

ISSCC 2023: GaN and Si combine to drive SiC at 1,700V

With their low losses, fast switching and high temperature tolerance, silicon carbide mosfets are now a viable option for high-current switching for use below 2kV. However, the field is relatively new and the ‘right’ way to drive such devices has yet to be established. At ISSCC 2023, National Yang Ming Chiao Tung University of Taiwan presented its version of an ...

ISSCC 2023: The processors that the IEEE wanted to hear about

A recent innovation at ISSCC is for the organisers to hand-pick a few ICs that they would like to hear about the conference – all the other speakers have to apply to present their innovations. This year they picked machine learning accelerators for both training and inference, an ultra-high bandwidth chip-to-chip link and an ‘infrastructure processing unit’ (IPU) for off-loading ...

6G – the next wireless communications standard

The fundamentals of next-generation wireless communications are in progress and commercial deployment is expected around 2030. This will enable new possibilities, including holographic applications, extended realities and digital twins, says Dr Taro Eichler. The prospect of offering large contiguous frequency bands to meet demand for extremely high data transfer rates in the Tbit/s range will drive the next generation of ...

ISSCC 2023: Point-of-load conversion at the next level

At ISSCC this week in San Francisco, the University of California and Murata described a way to take point-of-load conversion to the next level – two-stage conversion with vertical current paths and package-level integration. Point-of-load schemes have solved the problems of I2R losses across PCBs for a long time, but the traditional approach of putting the PoL converter next to ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News